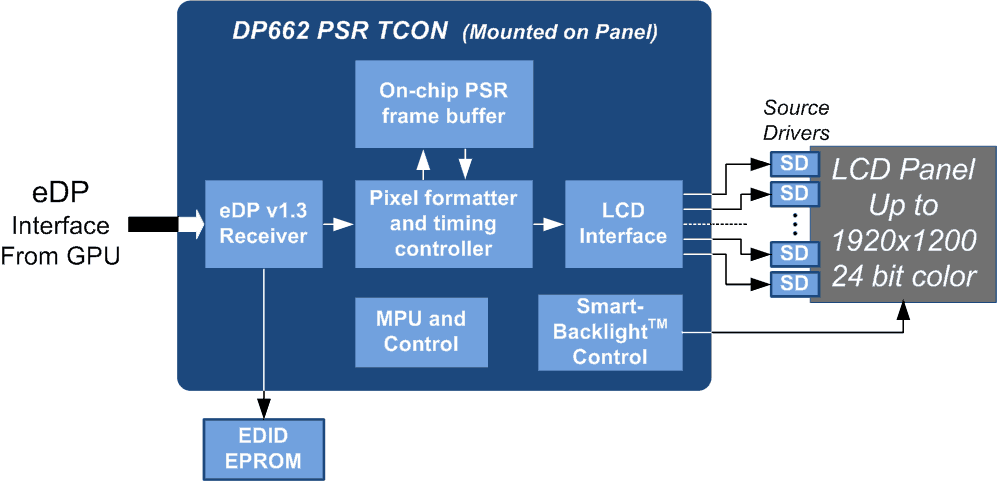

DP662 – 2 Lane eDP 1.3 PSR Tcon

– Not For New Designs –

eDP v1.3 LCD Timing Controller with PSR (Panel Self Refresh) and integrated frame buffer, Up To 1920×1200 Resolution

DP662 supports the PSR protocol in the Embedded DisplayPort™ Standard version 1.3 using an integrated frame buffer to minimize power. PSR eliminates the need for the CPU/GPU to send redundant video frames during static display images as this function is allocated to the Tcon using the integrated frame buffer. This enables the CPU/GPU to intermittently enter a low-power state, enabling net system power savings and thereby extending battery life in a mobile system.

Features

- Supports display resolutions up to 1920×1200

- Compliant to VESA® Embedded DisplayPort Standard version 1.3

- Includes backlight control through AUX

- 1.62 and 2.7Gbps eDP link operation with 1 or 2 lanes

- CrystalFree™ technology; no external clock reference required

- Supports full and fast link training, and no link training

- Up to 24 color bit depth RGB format input

- 6 or 8 component bit depth panel interface with FRC and gamma

- Internal color engine

- Programmable BIST and aging patterns

- Parade’s exclusive Smart-Backlight™ dynamic backlight control for color and power optimization

- Supports DisplayPort™ standard SSC 0.5% down spreading and additional spreading on Source Driver interface

- Supports point-to-point CoG panel-side interfaces

- Supports VESA Adaptive-Sync

- Supports eDP DRR/nvDPS/sDRRS power saving modes

- ASSR display authentication support

- ESD HBM 8kV

- VFBGA RoHs Halogen free package

Applications

- LCD Panels for Mobile PC platforms