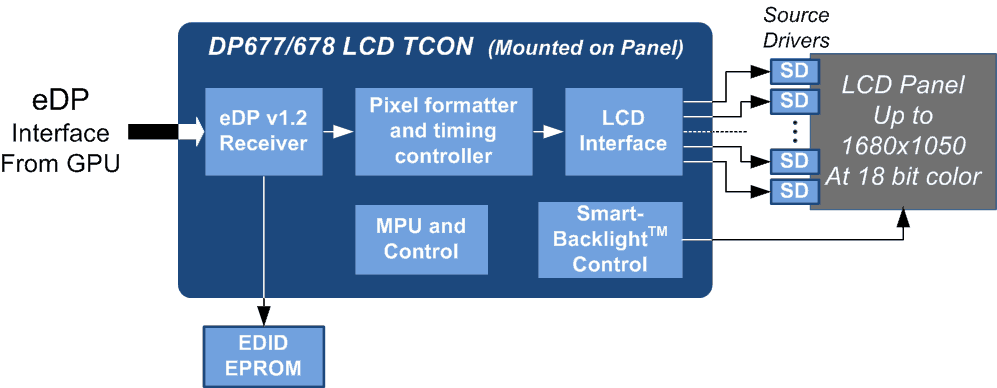

DP677 / DP678 — Very Low Power 1 Lane eDP 1.2 Tcons

Embedded DisplayPort™ v1.2 Timing Controllers, Very Low Power

DP677 and DP678 were developed with emphasis on very low power consumption, while supporting all of the necessary features of a timing controller for mobile and AIO PC applications. The devices support eDP 1.2 allowing backlight and other panel functions to be controlled through the eDP AUX Channel. They support a display resolution up to 1680×1050 with 18 bit color depth, or up to 1366×768 with 24 bit color depth. Back-side interface support to the LCD Source Drivers include mini-LVDS, Parade’s own SIPI® (Scalable Intra Panel Interface) CoG interface, and the support of other common CoG interface types that differentiate the DP677 and DP678.

Features

- Supports display resolutions up to 1680×1050 with 18 bit color depth, or up to 1366×768 with 24 bit color depth

- Compliant to VESA® Embedded DisplayPort version 1.2

- Includes eDP v1.2 backlight control through AUX

- 1.62 and 2.7Gbps eDP link operation with 1 lane

- CrystalFree™ technology; no external clock reference required

- Supports full and fast link training, and no link training

- 18 or 24 color bit depth RGB format input

- 6 or 8 component bit depth panel interface with FRC and gamma

- Internal color engine

- Programmable BIST and aging patterns

- Parade’s exclusive Smart-Backlight™ dynamic backlight control for color and power optimization

- Supports DisplayPort™ standard SSC 0.5% down spreading and additional spreading on Source Driver interface

- Multiple panel-side interface standards supported including

- Mini-LVDS

- Parade’s SIPI® (Scalable Intra Panel Interface) CoG interface

- Other common CoG interfaces

- Supports eDP DRR/nvDPS/sDRRS power saving modes

- ASSR display authentication support

- ESD HBM 8kV

- TQFN RoHs Halogen free package

Applications

- LCD Panels for Mobile PC platforms