PS8623 – DP to LVDS

DisplayPort™ to LVDS Converter

2 Lane DP input, Dual Link LVDS Output

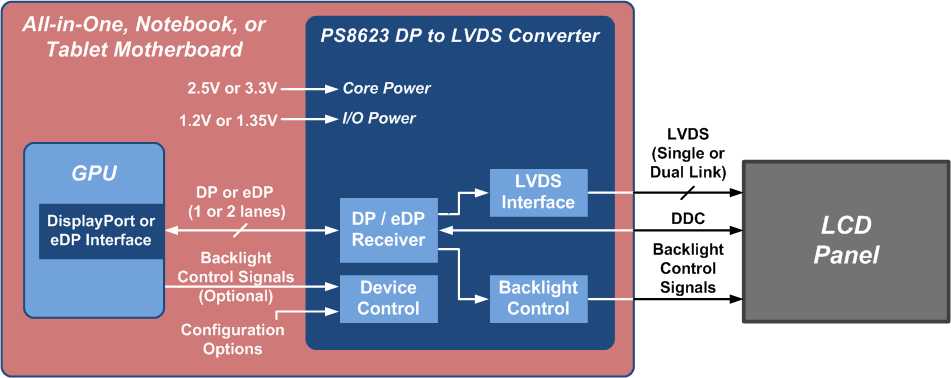

The PS8623 is a DisplayPort™ to LVDS converter designed for PC’s that utilize a GPU with a DisplayPort (DP™) or an Embedded DisplayPort (eDP™) output and a display panel that accepts an LVDS input.

KEY FEATURES

- Enables the use of LVDS display panels with DisplayPort™ or eDP™ video Source devices

- Supports up to 1920×1200@60Hz at 18-bit color depth

- No external crystal or timing reference needed with Parade’s CrystalFree™ technology

- Dual supply configuration requires 3.3V or 2.5V for I/O, and 1.35V or 1.2V for core

- Firmware-less operation, supports hardware pin configuration

- Optional I2C slave interface for chip control

- ESD: HBM 8kV at connector pins

- -20°C to 70°C Operating Temperature Range

- 7x7mm 48-pin QFN package (Halogen free, RoHS compliant)

DisplayPort Input

- Compliant to VESA® DisplayPort™ Specification 1.1a

- Supports 18, 24, and 30 bpp RGB color format input

- Compliant to VESA Embedded DisplayPort (eDP™) Specification 1.2 with AUX enabled backlight control

- Supports 1 or 2 lane main link configurations

- Link rates of 1.62Gbps and 2.7Gbps

- Supports various GPU specific power management protocols

- Supports all eDP display authentication schemes including ASSR

- Supports SSC 0.5% down spreading

- Supports full link training, fast link training, and no link training

LVDS Interface

- Single or Dual link LVDS output, clock speed up to 135MHz

- Supports up to 1920×1200@60Hz at 18-bit color depth

- LVDS spread spectrum clocking up to 2%

- Supports LCD panel power sequence control

APPLICATIONS

- All-In-One PC

- Notebook PC

- Tablet PC

The PS8623 will appear as a DP or eDP Sink device to the video Source, and will serve as an LVDS Source device to the LVDS display panel. The device is a fully integrated solution requiring no external CPU, memory, clock reference or voltage regulator. The PS8623 can be configured to read EDID from the display DDC channel. The PS8623 provides display panel power-up sequencing and backlight control including PWM generation. Backlight characteristics can be controlled by the video Source over the DP AUX channel using the eDP v1.2 DPCD control registers. Alternately, the video Source can provide the backlight control signals to the PS8623 which will gate them for panel power up sequencing, or the Source can bypass the device and control the panel backlight directly.