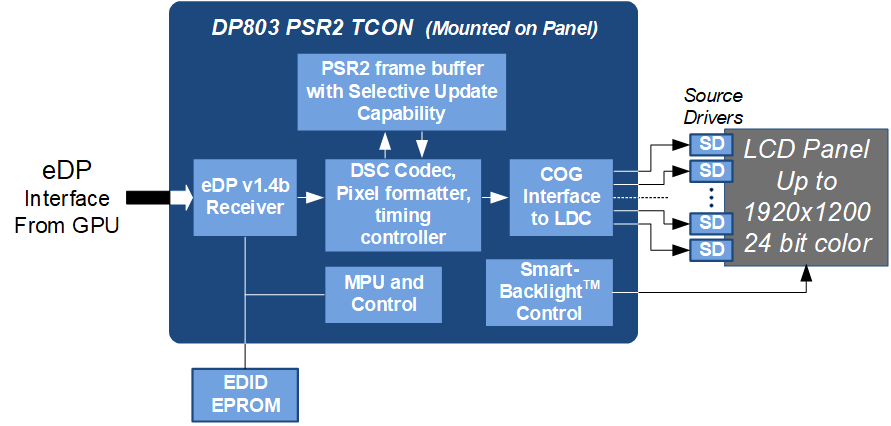

DP803 – 2 Lane eDP 1.4b PSR2 Tcon

eDP v1.4b LCD Timing Controller with PSR2 and Integrated Frame Buffer, Up To 1920×1200 Resolution

DP803 supports the PSR2 protocol in the Embedded DisplayPort™ Standard version 1.4b. The device enables a new level of power reduction by supporting all eDP 1.4b power saving features including PSR2 with Selective Update, Advanced Link Power Management (ALPM), and VESA® Display Stream Compression (DSC).

Features

- Embedded DisplayPort™ Input

- Compliant to VESA Embedded DisplayPort™ Standard 1.4b

- Supports 1 or 2 lane main link configurations and 2.7 or 1.62-Gbps link rates

- Supports full link training, fast link training, and no link training

- Supports 18/24-bit RGB color format input

- Supports DisplayPort™ standard SSC 0.5% down-spreading

- PSR (Panel Self Refresh)

- Supports Panel Self Refresh Ver. 1 (PSR) introduced in eDP v1.3

- Supports Panel Self Refresh with Selective Update (PSR2) introduced in eDP v1.4b, with or without AUX Frame Sync

- Supports Intel Media Buffer Optimization (MBO)

- Supports PSR/PSR2 with up to 1920×1200 resolution and 24-bit RGB color format

- Supports Single Frame Update

- Refresh Rate Switching Mode

- Supports seamless Display Refresh Rate Switching (sDRRS), Dynamic Refresh Rate (DRR), and nvDPS co-existing with PSR

- Supports Microsoft 48Hz video playback mode

- Support AMD Free Sync and VESA Adaptive Sync

- Supports Nvidia G-Sync (Direct Drive type G-sync)

- Content Protection

- Supports eDP authentication options: Alternate Scramble Reset (ASSR)

- Panel Interface

- Supports all sized panels up to 1920×1200, 18/24-bit RGB native color format

- Supports point to point COG interfaces up to 2D 4-ports (TQFN)/ 2D 6-ports (WFBGA) or 1D 6-ports

- COG interface pin swapping and internal data swapping offers flexible TCON PCB design

- Supports additional Sink-generated SSC clock modulation on COG interface: center spreading from 0.25% to 2.0%

- TCON Interface

- Supports dual gate and triple gate pixel structures

- Integrated TCON with programmable TCON control signal generation

- Fully programmable Row Driver and Column Driver control I/O

- Video Processing

- CrystalFree technology – no external timing reference needed

- Stores LUT contents in EEPROM to support Gamma Correction, Color Engine, and FRC

- Supports programmable BIST or Aging patterns

- Supports VESA Display Stream Compression (DSC)

- Backlight Control

- Parade’s exclusive Smart-Backlight™ feature for color and power optimization

- Control Interface

- I2C master for loading register initial values, or for functional expansion

- Hardware driven power management

- Built-in ESD Protection

- HBM 8kV, MM 400V, CDM 2000V

- Package Options

- 66-pin 5×10 mm2 TQFN RoHS halogen free package

- 102-ball 9×3.5 mm2 WFBGA RoHS halogen free package

Applications

- Notebook LCD panels

- Tablet LCD panels

- AIO LCD panels utilizing power saving PSR/PSR2 function